近十年来,高速数字技术在总线传输方式逐渐在向串行化方向发展,但在以各种中高端处理器为核心的中央处理和计算单元,目前主流仍然采用基于并行DDR总线架构的DRAM进行大数据量的运算。

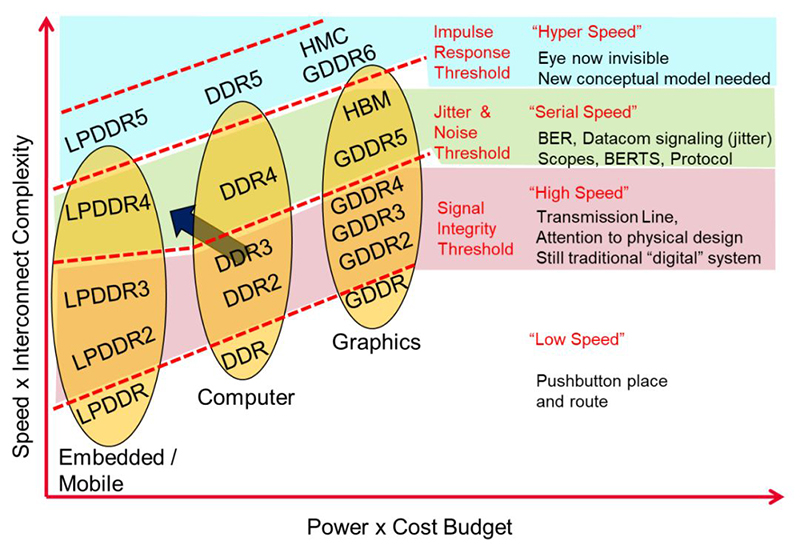

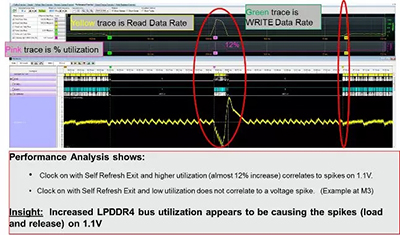

对于现代计算架构来说,DDR内存更加重要,CPU、GPU乃至TPU等其它类型处理器有海量的数据计算,也对存储器的吞吐速率带宽提出更大的要求,海量计算数据需要对DDR访问读写操作,若干年来DDR技术已经经历了DDR1~4,即将进入DDR5的时代,除此之外,还衍生出来图形计算总线GDDR,应用于GPU和FPGA等更先进的三维封装工艺HBM和HMC技术等等。目前计算机服务器行业主流还是以DDR4为主。下图展示了当前高性能内存技术的发展技术方向。

图1:高性能内存技术发展方向

逻辑分析仪在这些并行总线架构的测试和分析中,仍然有不可取代的作用。

本文将为大家介绍一下当今世界上技术最领先的逻辑分析仪U4164A在DDR4/LPDDR4逻辑总线测试上的应用。

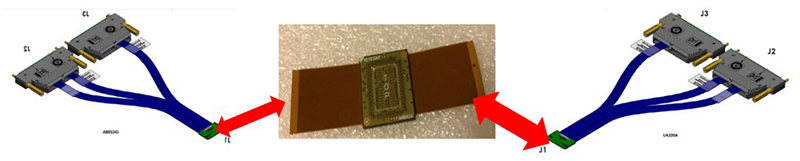

图2:DDR总线观测和分析方案

分析和探测设备:

U4164A逻辑分析仪模块和探测夹具

U4164A是采用AXIe总线的LA分析模块,单一模块达到136通道,可以支持3个模块同步达到402通道,满足DIMM等环境下的全总线采集分析。采用传统的同步采样模式,配备了02G选件的状态分析速率最高达到2.5Gbps,采用双采样模式或4采样模式时,支持的状态数据速率达到4Gbps,后一种模式通常用于DDR4/LPDDR4的状态分析和测试。U4164A也是业内唯一能够支持达到4Gbps以上的DDR4总线的解码和分析的逻辑分析仪方案。采用定时分析方式时,分析速率达到2.5GHz,如果采用1/4通道模式,定时分析速率可达10GHz。另外U4164A在满通道采样时,每通道最高可配置高达400Mpts采样深度,在1/4通道模式下,采样深度将达到1.6Gpts。 配合BGA Interposer或者DIMM Interposer及B4611A软件可以对DDR总线进行解码和分析。对于ONFi,FPGA也有相应的应用选件可以支持。

图3:配有3个模块的U4164A系统

上图是一配有3个模块的U4164A系统,采用Futureplus提供的DIMM Interposer,提供针对DDR4/LPDDR4总线的读写,命令和地址等全总线的观测和分析能力。

图4:DDR4 BGA Interposer W4631A/4633A和U4208/U4209A ZIF电缆

通常除了采用示波器进行电气层信号质量和基本时序参数之外,DDR总线的状态机复杂时序特性,以及总线的命令操作解析由于示波器固有的4通道限制需要通过逻辑分析仪辅助分析。是德科技的U4164A逻辑分析仪,同步分析速率可以达到4Gbps,采样窗口可以低至100mv x 100ps,单路采集样本高达400M,对于DDR4总线的的测试是非常合适的,另外配合B4661A 分析软件,可以解析DDR4会话操作,实现DDR4总线的命令解码,解析MRS,命令,行列地址,并可以直接触发物理地址捕获特定信号,利用深存储的大量样本,可以对DDR总线的性能进行分析,包括统计内存总线有效吞吐速率,统计各种命令操作以及总线利用率,分析对不同内存地址空间的访问效率。另外利用是德科技独有的逻辑分析仪内部眼图扫描功能,可以同时分析扫描总线各个比特位的眼图质量,在同步分析中调整合适的采样位置。

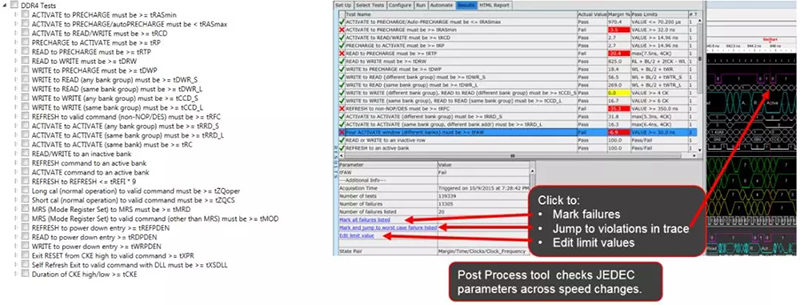

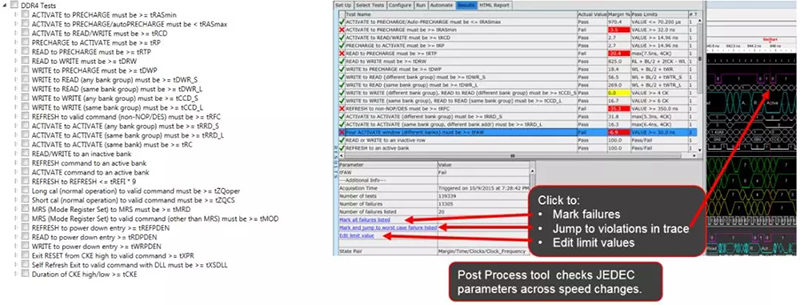

在JEDEC的规范中,除了用示波器能测试到的简单信号时序之外,还定义了如下图左侧大量总线状态的时序参数要求,B4661A软件可以支持这些参数的实时和后分析功能,分析判断测试结果是否符合规范的范围要求,并且可以跟踪测量结果,对于违规的测量参数可以跟踪到波形界面,从而定位命令和操作的根源问题。

图5:针对DDR4/LPDDR4总线的B4661A软件一致性分析

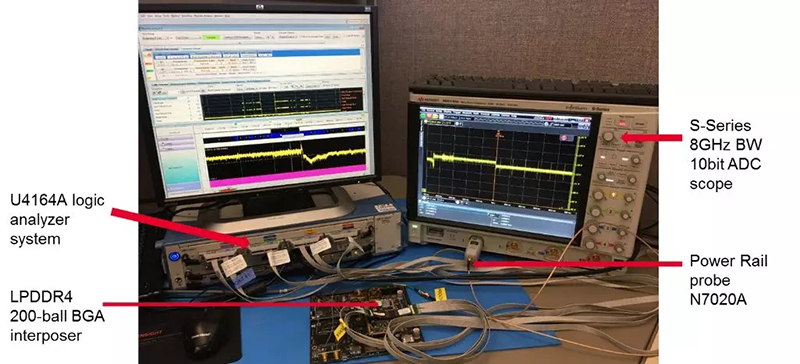

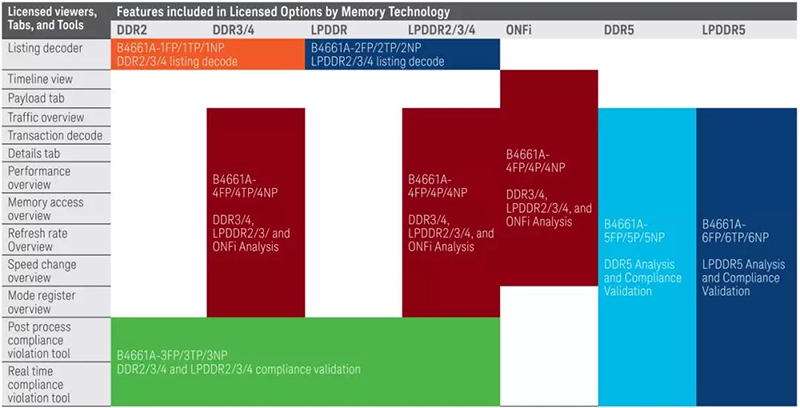

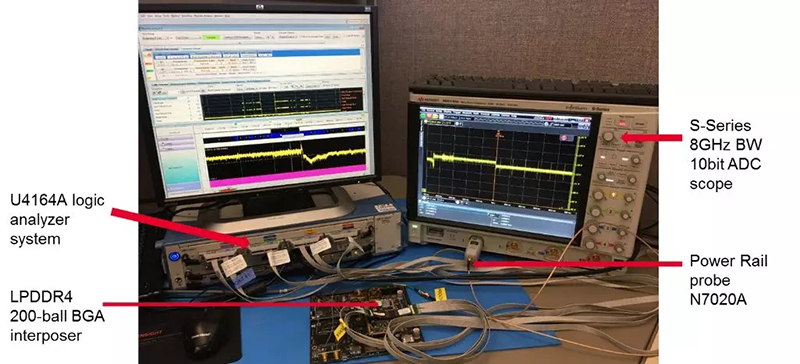

对于DDR系统中存在的复杂问题,还可以使用逻辑分析仪和示波器进行联合调试,逻辑分析仪优势在解析DDR总线会话和操作性能分析,示波器的强大在于信号波形的观测,也可以测量电源纹波和噪声。是德科技的逻辑分析仪自带的View Scope功能,可以通过网线和触发线,同步捕获示波器内的波形,时基相关的查看逻辑操作和物理波形的关系,下面的实测场景就是使用逻辑分析仪捕获LPDDR4信号,使用10比特的S示波器配合电源完整性测试探头N7020A,精确观测供电电压1.1V的实例,可以看到在逻辑分析仪界面,电源电压轨迹展开出现尖峰和跌落。

图6:U4164A逻辑分析仪和S示波器联合调试

再通过逻辑分析仪的内存软件解析DDR总线的操作和分析性能,可以分析出由于系统中集中的读操作,LPDDR4的速率切换导致的电源电压的波动,以及特定命令操作导致的电压跌落现象,下图我们展示了逻辑分析仪界面内总线交易解码、总线利用率时域统计和电压波形的同步显示,展开命令后可以发现在电压出现尖峰的周边是Clock重新打开、Self Refresh Exit操作,再看总线利用率的时域变化,突发的读操作总线利用率提升了12%,由于突发的连续读操作形成电源负载瞬间变化,导致1.1V上出现了瞬间的38mV的尖峰。这个电压波动可能导致系统工作可靠性下降,所以需要进一步改善DDR供电电源网络的设计。

图7:示波器和逻辑分析仪联合调试与分析的结果

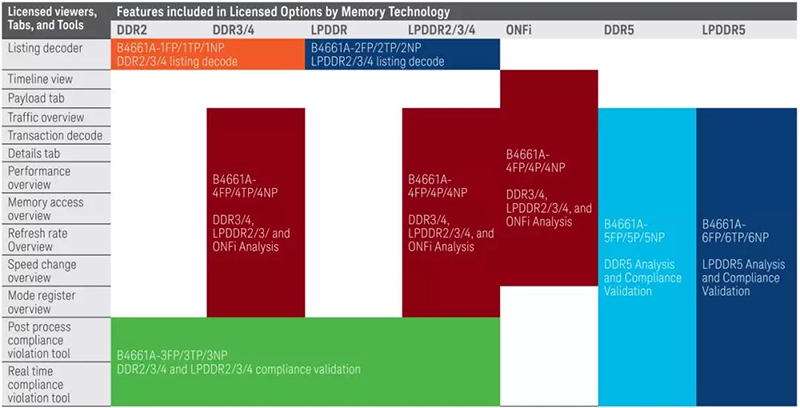

通过上述实例,可见逻辑分析仪U4164A+B4661A软件在DDR信号测试方面具有强大的分析功能和不可比拟的优势。

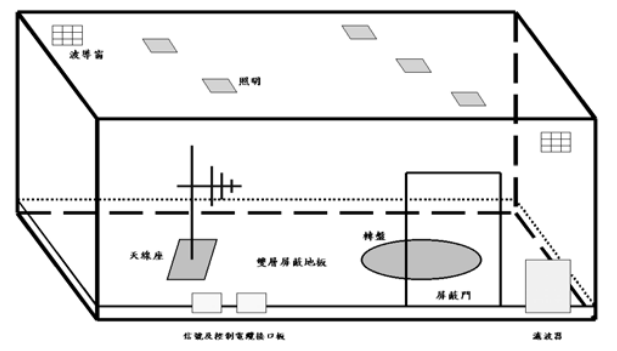

图8:B4661A软件对DDR总线的全面支持

型号 | 数量 | 说明 |

U4164A | 3/1 | 逻辑分析仪模块,DDR4 DIMM条测试配置数量3,测试颗粒配置数量为1 |

U4164A-02G | 3/1 | 2.5GHz状态时钟速率,4Gbps数据速率 |

U4164A-400 | 3/1 | 存储深度达到400Mpts,便于长时间捕捉总线异常成因 |

PS-X10-650-3PH | 1 | FS2520 DDR4 DIMM Interposer 用于DDR4内存条完整CMD/ADD/Data读写信号探测 |

W4643A-004 | 1 | DDR4 x4/x8 BGA interposer x 4 用于DDR4 BGA信号探测 |

W4641A-004 | 1 | DDR4 x16 BGA interposer x 4 用于DDR4 BGA 信号探测 |

U4208A | 1 | 探头电缆连接BGA Interposer左侧翅膀至逻辑分析仪 |

U4209A | 1 | 探头电缆连接BGA Interposer右侧翅膀至逻辑分析仪 |

M9505A或M9502A | 1 | 5槽/2槽机箱,DIMM配5槽,测BGA可配2槽 |

M9537A | 1 | 逻辑分析仪内置控制器,运行逻辑分析仪和DDR分析软件 |

B4661A | 1 | DDR及ONFi解码分析选件 |

B4661A-1FP | 1 | DDR解码分析及物理地址触发工具 |

B4661A-2FP | 1 | LPDDR解码工具 |

B4661A-3FP | 1 | DDR和LPDDR协议一致性测试工具 |

B4661A-4FP | 1 | DDR3/4和LPDDR2/4/4性能分析工具 |

B4661A-5FP/6FP | 1 | DDR5和LPDDR5协议分析和一致性测试工具 |

更多详细配置信息请咨询Keysight公司相关客户经理.

以上本文就DDR4/LPDDR4总线的协议测试从信号连接探测到捕获,以及分析做了一个简明的介绍。

当前随着并行总线速度的加快,探测和捕获难度呈几何级数上升。因此业界也有推出简化版的DDR总线协议分析仪产品,需要指出的是此类协议分析仪通常只能进行常规的命令和地址分析,未提供完整数据总线的接入和分析,因此不能与U4164A逻辑分析仪相提并论。