-

电子电力、信号、记录、磁场及核与辐射测量

- 电力电工仪器仪表及试验装置

- 交直流电桥 交直流电位差计 交直流检流计 万用表 钳形电流表 电参数测量仪、数字功计 功率分析仪 电能质量分析仪 兆欧表/绝缘电阻表 接地电阻表 电流探头、电流钳、罗氏线圈 电压探头、差分探头、光隔离探头 回路电阻测试仪 相序表 分流器 仪用互感器 相位伏安表 CAN传感器 电流传感器 电压传感器 传感器电源

- 交直流电源、负载等电力装置

- 直流电源 交流变频电源 直流电子负载 交直流电子负载 交流稳压器 调压器 隔离变压器 UPS不间断电源 逆变器 电阻负载箱 防孤岛负载 电抗器 电力变压器 功率补偿装置 交流源载一体机 源表、双极性电源 电池模拟器 源载系统(源载一体机)

- 安规、电器附件测试仪器及设备

- 耐压测试仪 绝缘电阻测试仪 接地电阻测试仪 泄漏电流测试仪 耐压绝缘测试仪 安规综合测试仪 测试手指 球压试验装置 弹簧冲击器 稳定试验台 漏电起痕试验仪 灼热丝试验仪 燃烧分析仪 针焰试验仪 脉冲线圈测试仪(匝间/层间绝缘耐压测试仪) 光伏安规测试仪

- 电子元件、半导体、集成电路仪器

- LCR电桥/LCR测试仪 阻抗分析仪 直流低电阻测试仪/微欧姆计/微电阻计 压敏电阻测试仪 晶体管图示仪 电解电容漏电流测试仪 变压器综合测试仪 二极管、三极管测试仪 电容测试仪 电感测试仪 热敏电阻测试仪 线束检测仪 瞬断检测仪 半导体特性分析仪 高阻计、绝缘电阻仪

- 音视频、射频、信号通讯网络仪器

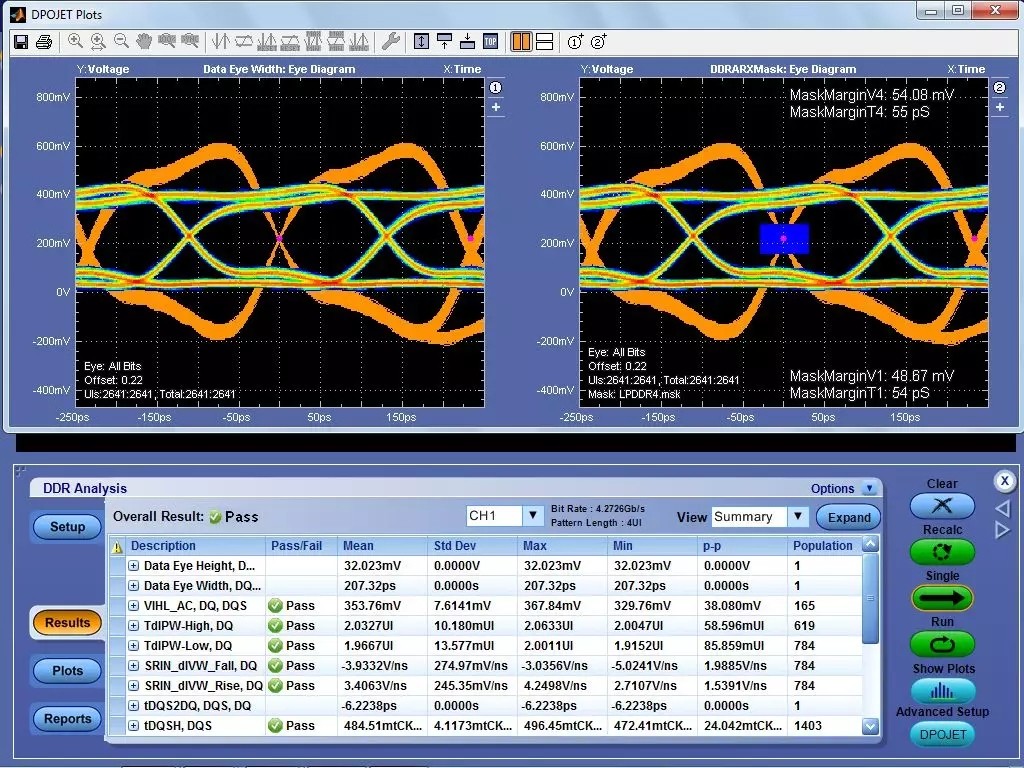

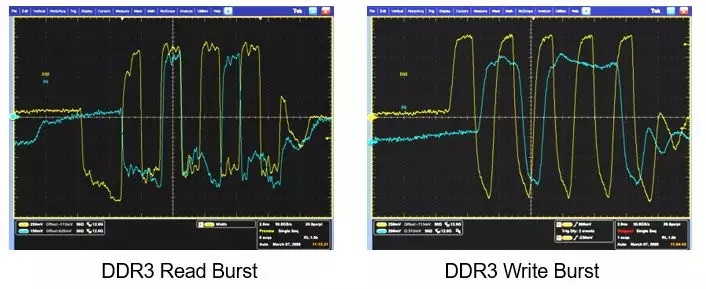

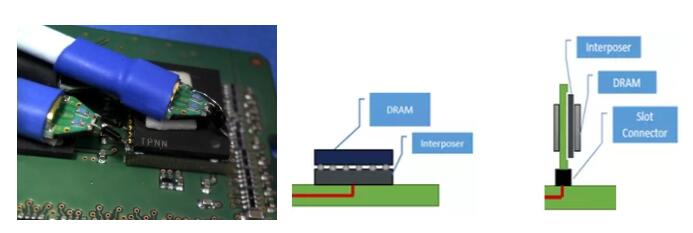

- 脉冲电压发生器 脉冲功率计 场强仪 频率特性分析仪 线缆认证测试仪 线缆传输性能测试仪 信号放大器 射频电流探头 屏蔽箱、屏蔽房 无线通信测试仪 扬声器极性测试仪 音频扫频仪 视频信号发生器 逻辑分析仪 网络分析仪 失真仪 毫伏表 低频信号发生器 音频分析仪 射频信号发生器 频谱分析仪 示波记录仪 数据采集器 函数/任意波形信号发生器 示波器

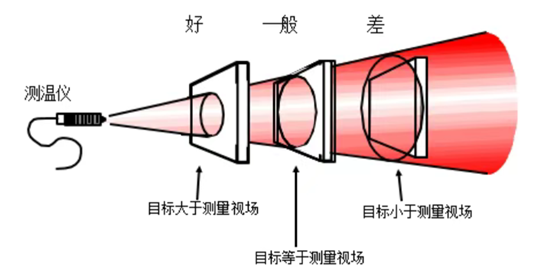

- 物理量、物化测量、热工环保测量

- 光学仪器、光电检测、光通讯仪器

- 材料、机械、环境、可靠性试验设备

- 理化分析、无损检测仪器、实验室装置

- 量具量仪、衡器、机械量仪表

- 工业过程自动化控制系统及仪表

- 行业专用仪器仪表、地球物理仪器及装置

- 电子工具、五金工具及辅助配套器具

- 仪器仪表配件、耗材、元件及结构装置

- 劳保、办公、照明、搬运用品及装置