一、概述

电快速瞬变脉冲群(Electrical Fast Transient Burst) 主要模拟电感性负载的切换、继电器触点弹跳等类干扰。在实际现场应用中,因其短时间内电压较高、重复频率较高、脉冲波形的上升时间短等特点,EFT具有很强的干扰性,往往会带来直接或间接的巨大代价。诸如产线报错停机影响生产,或干扰问题反复不定时出现降低客户满意度,所以EFT是电磁兼容测试中比较重要且容易出现问题的测试项目。

二、EFT的信号特征

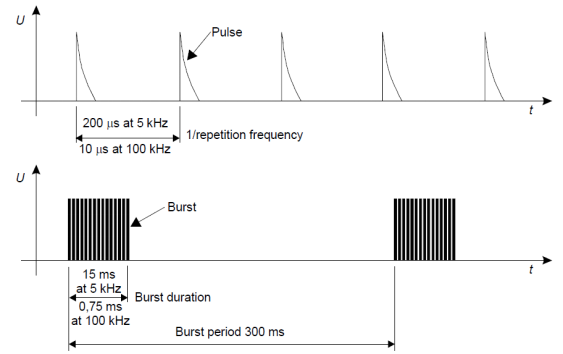

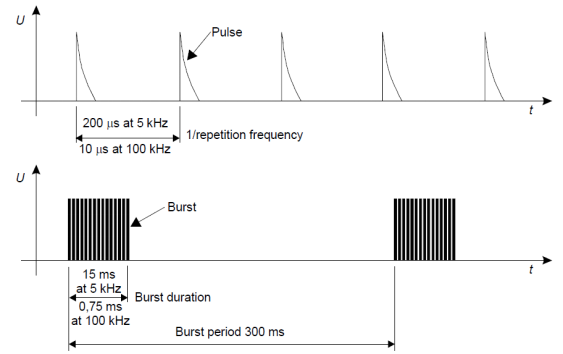

根据GB/T17626.4-2018/IEC 61000-4-4:2012 标准《电磁兼容试验和测量技术电快速瞬变脉冲群抗扰度试验》的单脉冲特征,如图1和图2所示:

(1)脉冲上升时间(从10% 上升到 90%):5×(1± 30%)ns ;

(2)脉冲持续时间(从上升沿的 50% 到下降沿的 50%)50×(1± 30%)ns ;

(3)在1000Ω负载时的峰值电压:0.25kV~4kV ;

(4)在50Ω 负载时的峰值电压:0.125kV~2kV。

(5)脉冲重复频率:5kHz 或者100kHz ;

(6)单脉冲群持续时间:

在5kHz 峰 值 电 压 时 :15×(1± 20%)ms ;

在 100kHz 峰 值电 压 时 :0.75×(1± 20%)ms ;

(7)脉 冲 群 的 重 复 周 期 :300×(1± 20%)ms 。

图1 电快速脉冲群概略图

图2 输出50Ω负载的单个脉冲理想波形(tr = 5 ns,tw = 50 ns)

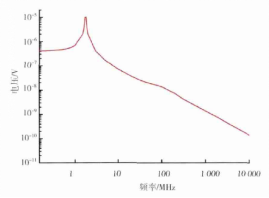

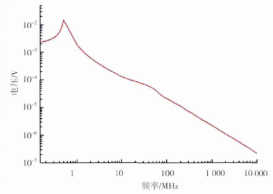

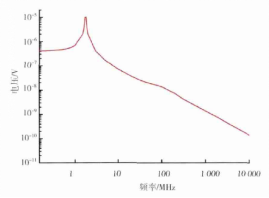

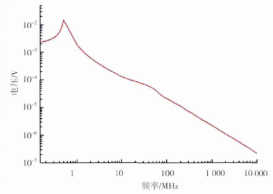

三、EFT频谱特性

参见图3和图4,分析EFT频谱特性可知:

(1) EFT信号的频率范围很宽,几MHz~几百MHz;

(2)干扰能量主要集中在40MHz以下;

(3)400MHz以上的信号,衰减很快,能量较小;

所以EFT干扰抑制设计时,一般考虑到400MHz左右就足够了。

图3 单个脉冲频谱

图4 5KHz脉冲群频谱

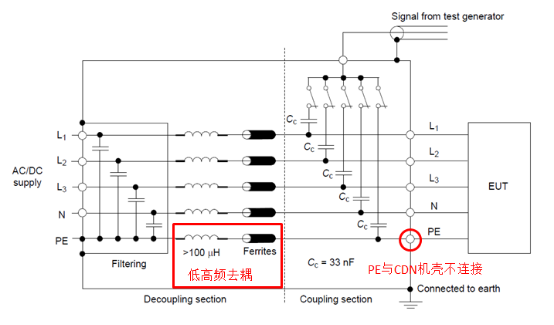

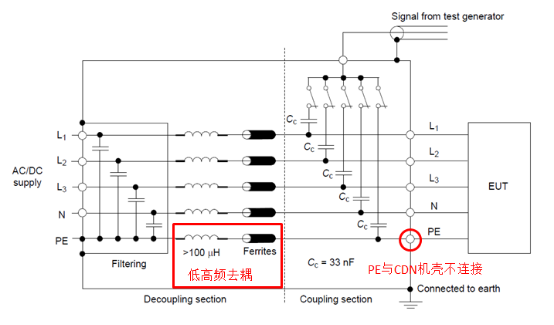

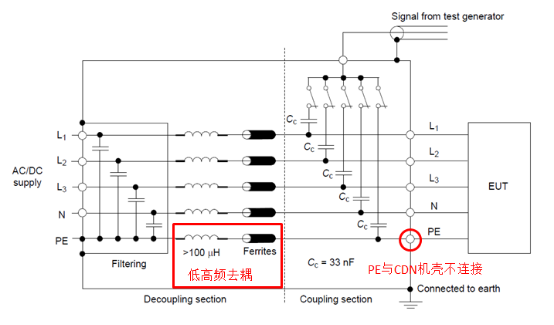

四、EFT测试电源端口CDN

EFT耦合方式为共模形式,为模拟实际应用中PE线较长和接地不可靠的情况下,设备对地阻抗较大,EFT测试用CDN中PE进行了去耦处理,这是与SURGE测试用CDN最大的区别,也是很多测试工程师容易忽视的地方,EFT测试用CDN参见图5所示。

图5 用于DC/AC电源端口/端子的耦合/去耦网络

EFT噪声耦合路径:信号发生器→耦合电容→电源端口→EUT→分布电容→信号发生器,参见示意图图6.

图6 EFT电源端口噪声耦合路径示意图

五、案例说明

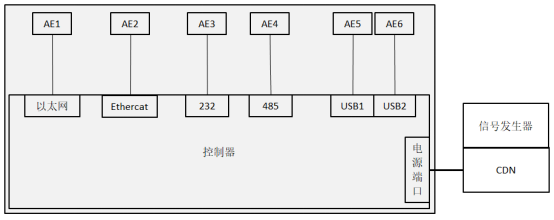

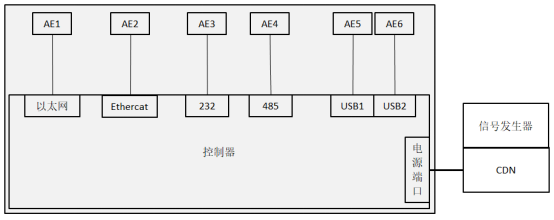

背景:某工控领域用控制器产品,对电源端口进行±2KV,100KHz的EFT试验时,整个控制器死机,出现以太网、EtherCat、232和485通讯超时及USB设备无响应等问题。控制器测试组网参见图7所示。

图7 控制器测试组网示意图

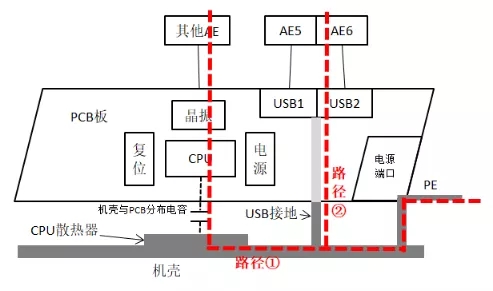

1.对电源的PE进行EFT干扰试验时,有意思的现象如下:

1)当插上USB设备,控制器不会出现死机状态,但会影响USB设备(AE5与AE6出现无响应);

2)当拔掉 USB设备,控制器出现死机(以太网、EtherCat、232和485通讯超时)。

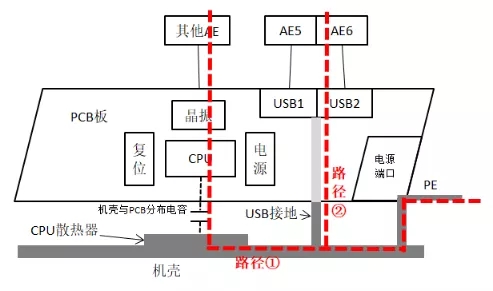

原因分析:路径①和路径②为噪声两条主要路径。当插上USB设备时,路径②使得一部分噪声分流,从而控制器不死机,但影响USB设备性能。当断掉路径②(拔掉USB设备),噪声主要通过①进行回流,使得控制器报错严重,甚至死机。路径分析参见图8和图9。

图8 控制器组网噪声路径示意图

图9 控制器空间结构与组网噪声路径示意图

2.拔掉USB设备,在控制器死机状态下进行分析与整改

1)从噪声回路分析可知,噪声是通过机壳与PCB间的分布电容,可能干扰了CPU及周围的晶振、复位电源等敏感器件,出现了死机现象。

注:CPU的散热器与机壳一体化设计,且CPU散热器紧邻CPU及周围敏感器件,CPU散热器与敏感器件间的分布电容与PCB其他部分相比较大。

2)去掉机壳后,进行PE线的EFT试验,不再出现报错及死机问题,验证了分析的正确性。

3.通过以上分析把思路聚焦到如何减小CPU散热器与敏感设备间的分布电容.

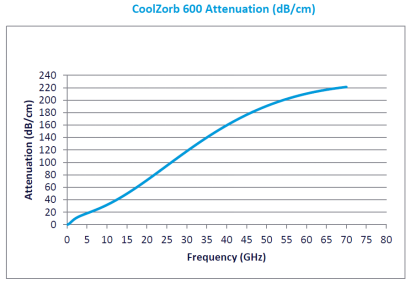

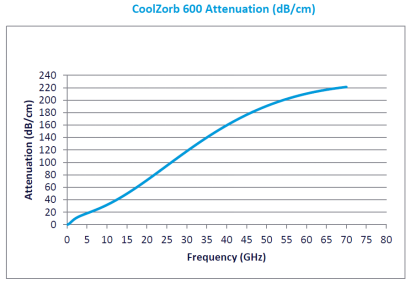

1)利用吸波材料来排查死机的根源,是CPU、晶振、复位还是其他器件受干扰导致的。吸波材料选择Laird家的COOLZORB_600系列,其衰减频率特性参见图10.

图10 CoolZorb Attenuation (dB/cm)

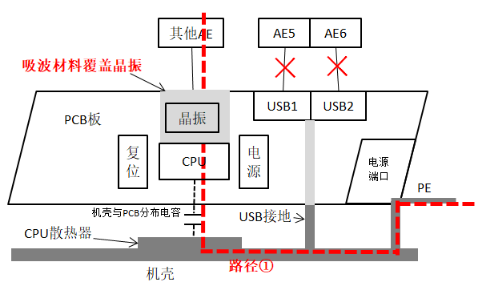

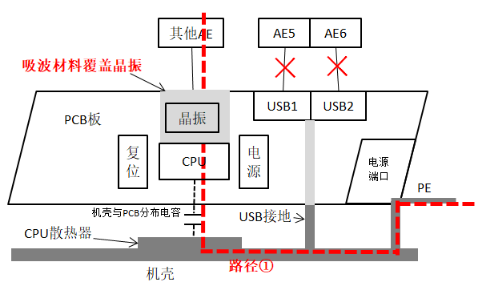

经过排查,当用吸波材料把晶振覆盖时,EFT测试无问题,确认是晶振受到了干扰,导致死机,参见图11。

图11 吸波材料覆盖晶振示意图

2) 将CPU散热器靠近晶振区域进行切割,增大空间距离,EFT测试无问题。

4.整改设计方案落地

综合以上整改手段,解决方案有三个:

1)将CPU散热器高度整体降低,增大与敏感器件的距离,从而减小分布电容,但会影响散热效果,不予采用;

2)用吸波材料对晶振器件进行覆盖,会增加成本(物料成本,组装成本等);

3)将CPU散热器靠近晶振器件处进行切割,增大与晶振的距离,不影响CPU的散热,也没有成本增长,为最终的设计落地方案,参见图12。

图12 CPU散热器靠近晶振处切割图

5.方案验证

恢复初始测试组网状态,进行各端口进行多轮次的EFT测试验证,结果无问题,确认方案可靠性。

六、思考与启示:

1.机壳地为滤波及屏蔽接地设计的低阻抗参考点,同时也是噪声回流路径,机壳地上会有很大的噪声电流流过。机壳地上的噪声电流会通过感性或容性耦合干扰邻近的敏感设备或器件;

2.系统化分析与定位问题根源,并要善于利用吸波等电磁性料来辅助分析问题,提高效率。

3.分布电容本质上是场分析的等效转化,所以吸波材料影响了场分布,从而影响结果;

4.机壳金属结构,尽量远离敏感器件(例本文中的晶振器件),且尽量避免直角棱边结构而引起的尖端效应。